# GBCS Scheme

| USN |  |  | 15CS32 |

|-----|--|--|--------|

|-----|--|--|--------|

# Third Semester B.E. Degree Examination, Dec.2016/Jan.2017 Analog and Digital Electronics

Time: 3 hrs. Max. Marks: 80

Note: Answer FIVE full questions, choosing one full question from each module.

## Module-1

- 1 a. Explain the working of N channel DE MOSFET, with the help of neat diagram.

- b. With circuit diagram, explain any two application of FET.

(08 Marks) (06 Marks)

c. How CMOS can be used as inverting switch?

(02 Marks)

#### OR

2 a. Design a voltage divider bias network using a DEMOSFET with supply voltage  $V_{DD} = 16V$ ,  $I_{DSS} = 10 \text{mA}$  and  $V_P = 5V$  to have a quiescent drain current of 5 mA and gate voltage of 4V. (Assume the drain resistor  $R_D$  to be four times the source resistor  $R_S$  and  $R_2 = 1 \text{k}\Omega$ ).

(08 Marks)

b. Explain the performance parameters of Op-amp.

(08 Marks)

# Module-2

3 a. Minimize the following Boolean function using K – map method

$f(a, b, c, d) = \sum m (5, 6, 7, 12, 13) + \sum d (4, 9, 14, 15).$

(06 Marks)

b. Apply Quine Mc – Clusky method to find the essential prime implicants for the Boolean expression  $f(a, b, c, d) = \sum m (1, 3, 6, 7, 9, 10, 12, 13, 14, 15)$ . (10 Marks)

#### OR

- a. A digital system is to be designed in which the month of the year is given as input is four bit form. The month January is represented as '0000', February as '0001' and so on. The output of the system should be '1' corresponding to the input of the month containing 31 days or otherwise it is '0'. Consider the excess number in the input beyond '1011' as don't care conditions for the system of four variables. (ABCD) find the following:

- i) Write truth table and Boolean expression in SOP  $\Sigma m$  and POS  $\Pi M$  form.

- ii) Using K map simplify the Boolean expression of canonical mini term form.

- iii) Using Basic gates implement logical circuit.

(10 Marks)

b. What is Hazard? List the type of hazards and explain static 0 and static - 1 hazard.

(06 Marks)

### Module-3

- 5 a. Implement the following function using 8:1 multiplexer  $f(a, b, c, d) = \sum m (0, 1, 5, 6, 8, 10, 12, 15)$ .

- b. Realize the following function using 3:8 decoder

- i)  $f(a, b, c) = \sum m(1, 2, 3, 4)$

- ii)  $f(a, b, c) = \sum m(3, 5, 7)$ .

(04 Marks)

c. What is Magnitude Comparator? Explain 1 bit magnitude comparator.

(06 Marks)

#### OR

6 a. Design 7 – segment decoder using PLA.

(08 Marks)

b. Differentiate between Combinational and Sequential circuit.

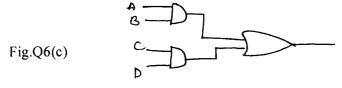

c. Write VHDL code for given circuit.

(04 Marks)

Module-4

- 7 a. What is Race around condition? With block diagram and truth table, explain the working of JK master slave flip flop. (10 Marks)

- b. Give State transition diagram and characteristics equation for JK and SR Flip Flop. (06 Marks)

OR

8 a. With neat diagram, explain Ring counter.

(04 Marks)

b. What is Shift Register? With neat diagram, explain 4 bit parallel in serial out shift resisters.

(08 Marks)

c. Compare Synchronous and Asynchronous counter.

(04 Marks)

# Module-5

- 9 a. Define Counter. Design A synchronous counter for the sequence 0 → 4→1→2→6→0→4 using JK Flip Flop.

(12 Marks)

- b. Explain Digital clock, with neat diagram.

(04 Marks)

OR

10 a. Explain the Binary ladder with Digital input of 1000.

(06 Marks)

b. Explain 2 bit simultaneous A/D converter.

(10 Marks)

\* \* \* \* \*